(1)准备

导入网表前,先设置一下焊盘路径(如果之前曾经设置过,理论上软件就记录了,不需再次设置)

找到封装和焊盘路径设置,个人建议,最好把常用的功能设置到favourite,

笔者的favourite不是很多,但是可以供大家参考一下,我的favourite如下

(2)导网表

导入网表,File-import-logic,首先讲第一方网表(用Orcad导出)

这里主要讲解右边的的区别

这里个人建议操作如上图,常规是忽略Fixedproperty,否则如果有固定属性则无法导入网表导致失败。

第三方网表本人没用过来导入allegro画板,毕竟第三方网表无法用orcad交互布局(可以通过抓取和PDF实现布局,非常好用,这个在后面allegro进阶教学会讲)

设置界面如下

(3)对症下药“医治”

这里讲一下,大部分人遇到的导入网表失败的例子,其他的问题就麻烦大家查看相关资料了,推动大家自觉了,哈哈!

1.缺少封装

这种没办法,封装你都没有了,赶紧做一个呗!

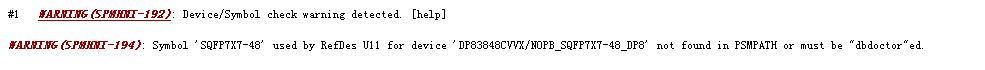

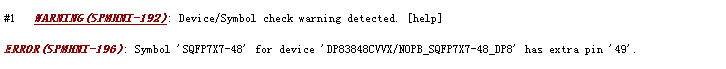

2.有封装但是封装引脚不对应

封装加散热焊盘,,导致焊盘数量不一致。

封装的固定脚采用常规焊盘而不是机械焊盘,导致焊盘数量不一致

3.封装都有然后什么都对但是还是出错

这种情况可以试试DB一下,上UpdateallDRC,然后Check,一次Check时可能会弹出Log窗口显示一些错误,不用管,第二次Check就没有了,神奇吧。

4.其他

错误的类型比较多,这里就不一一列举,出错的时候会弹出

在里面会详细列出错误的原因,到时候对症下药即可导入PCB了,

最后要真正到达complte没有error弹出来,才是真正网表真正导入成功了。

有兴趣学allegro的同学或者朋友,谢谢大家的阅读!

原创文章,技术分享!

有问题的不懂的可以留言大家讨论,谢谢大家支持!