在DC/DC芯片的应用中,我们需要提前来规划EMC的设计,避免在后期把太多的时间和精力花在整改和优化上。

说到EMC优化设计,我们要从EMC的三要素来分析和考虑:干扰源→耦合路径→敏感设备。我们通过抑制干扰源、切断耦合路径、保护敏感设备三个措施,来优化EMC设计。在DC/DC芯片应用中,DC/DC芯片通常是系统中常见的干扰源,我们主要从DC/DC这个干扰源的抑制来优化EMC设计。

在DC/DC电源中,Buck是最常见的电路拓扑,我们以Buck为例分析噪声源。Buck电路的主要噪声源是高频电流环路(Hotloop)和高频开关节点(SWnote),包含了比较宽频段的谐波分量,如图14.23所示。

图14.23高频电流环路(Hotloop)和高频开关节点(SWnote)

高频电流环路和高频开关节点分别产生时变的磁场和电场,其在PCB中的位置如图14.24所示。

图14.24高频电流环路和高频开关节点PCB中位置

以Buck电路为例,输入电流环路有梯形波的di/dt波形,而电感上存在三角波的di/dt,我们以近场磁场探头去看,输入电流环路的上下两个MOSFET附近的磁场强度远大于电感附近的,特别是高频部分。这是因为梯形波比三角波的高频分量更多,电流变化的斜率更快。所以通常对环路中di/dt的分析,我们更多的集中在输入电流环路,通常也称高频电流环路。

同样,Buck电路中,在SW节点上,会存在方波的dv/dt波形,该节点会产生电场。通常会容易忽略掉电感的dv/dt,事实上,在近场电场的影响中,电感本身并不是稳定的电位,具有较大的dv/dt分量,在单杆测试中尤其明显。

抑制高频电流环路引起的噪声源我们应如何分析抑制高频电流环路的引起的噪声源?我们可以将高频电流环路看成是磁偶极子,磁矩,磁场强度随着电流和环路面积而增大,那么可以通过降低电流和减小面积来实现。

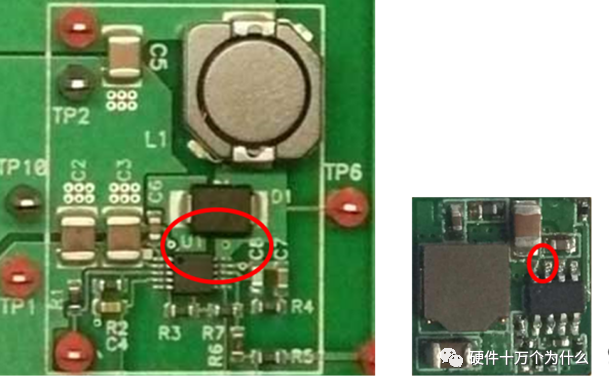

首先,我们需要找出不同拓扑的高频电流环路。如图14.25所示,红色的环路便是di/dt变化比较大的电流高频环路,可以看到BUCK电路,电流高频环路存在于输入电容和两个开关管(或者一个开关管和一个二极管)形成的闭合环路,而BOOST电路作为对偶拓扑,电流高频环路存在于输出电容和两个开关管。而SEPIC电路的电流高频环路存在于两个开关管和两个电容形成的环路中,如图14.25所示。

可以看到高频电流环路存在于开关管和连接开关管的电容形成的回路,因为电流变化最剧烈的通常在开关管之间,电流是在两个开关管之间切换,而通常电感由于电流不能突然变化,di/dt受到限制,而不是我们重点考察高频电路环路的部分。

图14.25几种拓扑的高频电流环路

找到高频电流环路后,我们需要抑制该噪声源引起的近场磁场。最有效的方式就是减少该环路的面积,通常电流大小需要满足功率输出的要求,不能随意减小。

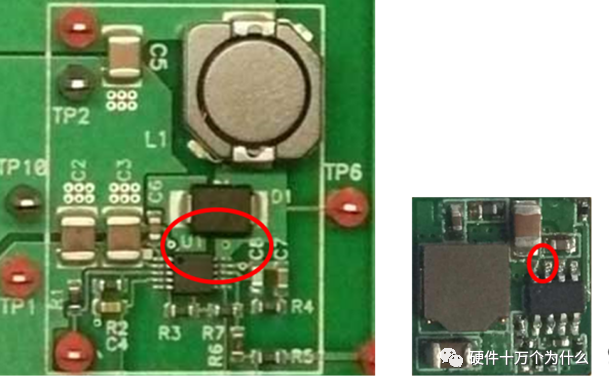

最简单的方式就是选用集成MOSFET的同步Buck电路,如图14.25(a),来替换非同步的Buck电路,如图14.25(b)。选用同步的SOT23-8的Buck芯片,输入电容可以靠近芯片放置,高频电流环路远小于左边的非同步BUCK,对外的辐射要小很多。

(a)(b)

图14.26非同步Buck与同步Buck布局对比

对于高频电流环路来说,减小环路面积还要特别注意输入电容的放置,如图14.27所示,将电容放置在芯片背面(减小了和开关管的距离),所测得噪声大小要远小于其他两种方式(电容放在侧面和用较长的引线连接电容)。

图14.27不同电容情况的辐射对比

随着先进封装的发展,更多的芯片将输入电容集成到芯片中,可以进一步减小高频环路的面积,以获得更好的EMC特性,如图14.28所示。

图14.28芯片集成电容的辐射情况

分别测试集成电容和未集成电容的两颗芯片A和B,同样的芯片和PCB布局,可以看到CISPR25传导高频部分,集成电容的芯片具有更低的高频噪声,具有较大的优势通过传导测试。

通过优化PCB布局,也可以抑制高频电流环路的噪声,其中一个方法就是通过底部铺铜。由楞次定律可知,感应电流具有这样的方向,即感应电流的磁场总要阻碍引起感应电流的磁通量的变化。如果PCB的TOP层为高频电流环路,会形成磁场,同样在下方的PCB铺铜中,也能感应处相反的磁场,从而抵消上面的高频电流环路引起的磁场。完整的铺铜距离高频环路越近,对磁场的削弱作用越强。那么我们要确保的是这个下方的PCB铺铜足够低的阻抗链接到GND,否则范围会帮助辐射。

抑制高频开关节点引起的噪声源在前面的分析中,BUCK电路中还存在高频开关节点(SWnote),这里的dv/dt会产生电场,也会产生辐射,同时引起的共模电流也会在传导测试中占据重要分量,尤其是在CISPR25的测试中。高频开关节点常常和辐射相关,尤其是在单杆天线测试和双锥天线测试中,在单杆天线测试中,高频开关节点产生的近场电场直接可以通过单杆天线接收。

抑制高频开关节点的dv/dt,首先可以通过减小面积来减小近场电场的电场强度。如图14.32,通过减小SW的铺铜面积,电场强度有了明显地减小。同样的方法,可以在单杆测试中,可以通过减小SW铺铜或者电感的体积来实现。前面我们分析过电感并不能保持稳定的电位,也是高频开关节点。

图14.32减小SW的铺铜面积,电场强度明显地减小

当功率受到限值的时候,电感体积不能明显的减小,可以选用屏蔽电感。这里的屏蔽电感是指外部有金属层作为屏蔽层并接地的电感,并不是指铺铜的一体成型磁屏蔽的电感。汽车级IHLE集成式电场屏蔽电感器一般具有金属外壳,使用时需要外壳接地,提供一个稳定的零点位,可以达到电场屏蔽的效果。

实测屏蔽电感的单杆天线测试(150K~30M),可以看到使用屏蔽电感后,有将近20dB的抑制效果,如图14.33所示。当然,实际中我们可以用金属罩对SW节点和电感进行屏蔽。

图14.33使用屏蔽电感抑制效果

我们知道共模电流在传导和辐射测试中会存在,尤其在辐射测试中,占据重要分量,需要对共模电流进行抑制。分析共模电流的路径,我们可以通过3种方式抑制共模电流。

(1)减小dv/dt的开关面积和电感尺寸,减弱电场的场强。

(2)屏蔽SW节点和电感,为dv/dt噪声源提供零电平,减小耦合电容。

(3)在输入端加共模电感,增加共模环路的阻抗。

1.1.3通过扩频抑制噪声源前面我们对噪声的频谱进行了分析,通过傅里叶分析,将时域的噪声转换到频域的能量包络。通过接收机或者频谱分析仪,我们可以得到每次谐波的能量大小,可以看到能量都集中到开关频率和它的倍频上,能量非常集中。

扩频技术就是通过将开关频率分布到周边的频段,来降低该频率点的能量峰值,比较方便地降低噪声源的能量集中度。如图14.34所示,就是最典型的三角波调制扩频,通常在原开关频率基础上,在开关频率在范围内,按照的调制频率变化。其中,通常又称调制的深度。

图14.34三角波调制扩频

我们以450kHz的开关频率为例,用10%的调制深度,将开关频率分布到405kHz~495kHz之间,这样在总的噪声总功率不变的情况下,基波分量被分摊了,降低了开关频率处噪声的能量。如图14.35所示,从左到右依次为无扩频、调制深度2.5%和调制深度10%的效果,经传导测试对比,可以看到没有扩频,能量非常集中,2.5%的调制深度已经可以满足限值要求,10%的调制深度有了更大的裕量。可以看到通常调制深度越大,调制效果越好,说明能量谱分布得更加宽,在实际应用中,还要考虑开关频率范围太宽可能会带来环路稳定性的挑战。同样不同的调制频率也会影响实际的扩频效果,需要综合来考虑。

图14.35没有扩频和两种扩频深度的传导测试对比

细说Buck【0】关于“Buck”为什么叫“Buck”

细说Buck【1】工作过程

细说Buck【2】工作波形1

细说Buck【3】CCM、DCM、BCM

细说Buck【4】输入电容

细说Buck【5】Buck电路的损耗

细说Buck【6】输出电流如何检测的

细说Buck【7】输出电容

细说Buck【8】Boot电容(自举电容)

细说Buck【9】输出电感

细说Buck【10】电源设计的意识流

——书籍推荐——

本专辑【细说Buck】会收录到硬十第三本书中