本文介绍一些verilog实现的数字电路的实例。如有错误,欢迎指出,感谢。

1

PLL复位电路

实验原理:通过异步复位同步释放来防止亚稳态的发生,PLL是锁相环,可以方便管理多个时钟。

Experimentalprinciple:Theoccurrenceofm,whichcaneasilymanagemultipleclocks.

2

乘法器

实验原理:多位的二进制从低位开始相乘,然后每次相乘后向前移动一位,这些结果然后相加,以下的实现是反向的,在每次运算后寄存器向后移动一位然后到最后一位的时候就到了第一位数据了。

Experimentalprinciple:Multi-bitbinaryismultipliedfromthelowbit,,,thefirstdataisreached.

3

状态机

实验原理:状态机三种不同的写法在于输入输出状态的位置。一段式是三个都写在一起,二段式是组合逻辑和时序逻辑分开写,三段式是三个都分开写。

Experimentalprinciple:Thethreedifferentwaysofw,two-segmenttypemeansthatcombinationallogicandsequentiallogicarewrittenseparately,andthree-segmenttypemeansthatallthreearewrittenseparately.

一段式电路图:

One-segmentcircuitdiagram:

二段式电路图:

Two-segmentcircuitdiagram:

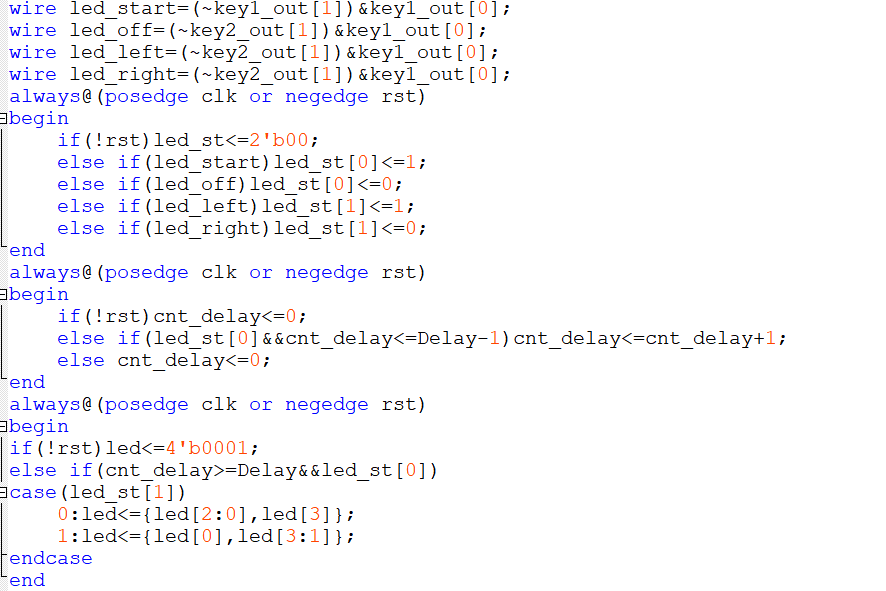

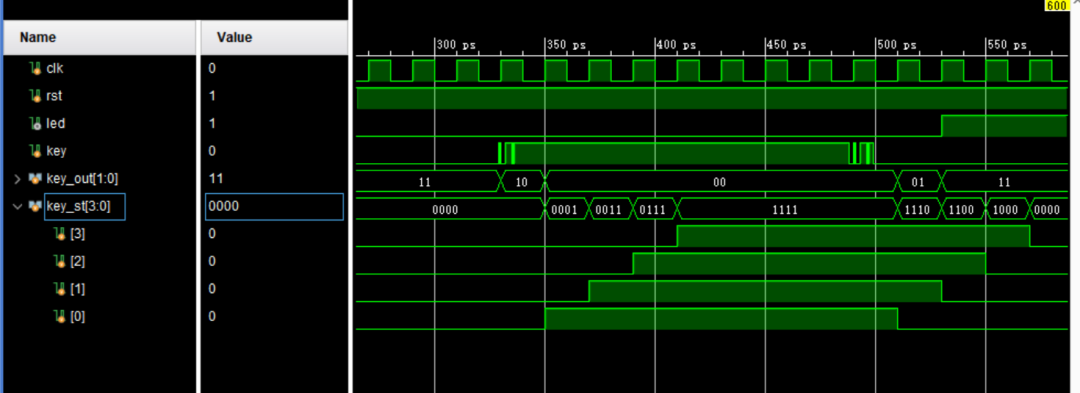

拓展:使用4个按键控制流水灯的四种状态,关闭,开启,左移,右移。按键的控制和以上类似,根据各个按键值的判断输出不同的流水灯控制信号。

仅给出核心代码:

Expansion:Use4buttonstocontrolthefourstatesofthewaterlight,turnoff,turnon,moveleft,,anddifferentflowlightcontrolsignalsareoutputaccordingtothejudgmentofeachbuttonvalue.

Onlythecorecodeisgiven:

参考资料:

《FPGA/CPLD边学边练》吴厚航著

翻译:谷歌翻译