硬件详细设计说明书

硬件详细设计说明书

引言编写目的本文档主要是为CPCI信号处理板卡的硬件设计做出详细的设计指导。

参考相关文档《信号处理板技术质量协议.doc》、A0、客户

术语和缩写词列出本文件中用到的专门术语的定义和外文首字母组词的原词组。

缩略语(专门术语)全称

缩略语(专门术语)

全称

CPCI

CompactPCI

FPGA

FieldProgarammableGateArray

ADC

Analog-to-DigitalConverter

DAC

Digital-to-AnalogConverter

单板结构概述该单板是一块以CPCI-6U为标准设计的信号处理板卡。信号处理板主要由信号处理单元、时钟单元、电源单元、接口单元和监测单元组成。具体将完成以下功能的设计:3路千兆以太网设计,用于接收监控参数和上报状态;4路串口设计,RS-422电平,用于接受和发送指令信息;2路时钟输入,用于产生D/A时钟、A/D采样时钟;1路模拟信号输出,频率范围:55MHz~660MHz;2路模拟信号输入,频率范围:55MHz~660MHz;2路数字光纤数据输入,速率不低于6.25Gbps;2路数字光纤数据输出,速率不低于6.25Gbps;FPGA设计,用于调制信号产生及解调;Flash设计,用于数据装订;ARM设计,解析网络协议或操作系统运行;

单板框图单板系统框图

关键器件列表

名称

用量

功能描述

商家

XC7Z045-2FFG900I

1

DualCortex-A9800MHzKintex-7-2GTX:16lanes

Xilinx

MSP4305438AIZQWT

1

MCU16bitRISCCPU

TI

MT41K256M16HA-125IT

2

DDR34Gb256M*16

MICRON

HTS1302-LH-001

2

10.3125Gbps单通道光模块

中航光电

AD9739

1

ADI

AD9643BCPZ-250

1

ADC14BITSRL250MSPS

ADI

AD9518-0ABCPZ

1

CLOCKGENVCO+

ADI

ADCLK914BCPZ-WP

1

CLKBUFFER1:1

ADI

功能模块划分根据第二章的框图,单板功能可划分为FPGA信号处理模块、AD/DA模拟信号模块、MCU电压监测模块、电源模块、时钟复位模块。

详细设计根据第2章的系统框图,详细描述每个模块所完成的主要功能,各个模块的设计细想,性能指标,实现方法。

FPGA信号处理单元FPGA信号处理单元使用一片XC7Z045-2FFG900I,内部包含ARMCortex-A9和FPGAK7,ARM部分主要完成系统运行功能,FPGA完成逻辑控制和高速接口功能,内部通过AXI总线相连。FPGA通过GTXBANK与板上2个10.3125Gbps的HTS1302-LH-001光纤接口通信;通过HP、HRBANK的LVDS信号控制模拟部分高速ADC、DAC芯片实现高速中频信号采集和输出。FPGA包含有3路RGMII千兆以太网,完成监控参数的接收和状态上报、4路RS-422完成指令收发、两路RS232用于调试、JTAG链路下载、以及接到连机箱内其他板卡的LCD、按键、LED、IO的GPIO外围电路实现LCD显示功能、按键控制LED灯信号控制和其他预留功能。

上电时FPGA从两片128MQSPIFLASHS25FL128SAGMFIR0加载程序,系统运行存储在2片4GbDDR3MT41K256M16HA-125IT中,系统存储在2GBeMMCNANDFlashMTFC2GMDEA-0M。FPGA通过IIC接口与MSP430交换数据和命令,同时还连有启动监测管脚、IO管脚和复位管脚用于重新加载和中断复位信号。运行环境使用。下表将列出详细项:

模块间接口及功能列表

通信对象

信号名称

接口形式

输入/输出

备注

其余设备

RS-422

J30J

双向

控制指令收发

千兆以太网

HJ30J

双向

监控状态参数接收与上报

MSP430

I2C

板内互联

双向

监控参数、状态等收发

后端信号

处理板

光纤通道

SFP

双向

将预处理后端数据发送到后端模块中;

接收后端模块发送的数据,通过处理后通道DA发出。

射频通道

中频输入

SSMA

输入

两路输入

射频通道

中频输出

SSMA

输出

一路输出

频综

参考时钟

SSMA

输入

两路输入,分别提供给ADC和DAC使用。

指标要求列表

功能项

相关指标

RS-422

速率≥1Mbps,通信协议自定。

光纤信号

通道数量:≥2,速率:最大支持10.3125Gbps。

中频输入

频率:55MHz~660MHz,采样率:≥55MHz,通道:2,有效位宽:≥10bit

中频输出

频率:630MHz~660MHz,采样率:≥1.6GHz,通道:≥1,位宽:≥12bit

频率:50MHz~90MHz,采样率:≥360MHz,通道:≥1,位宽:≥12bit

参考时钟

频率:ADC55MHz;DAC:1.6GHz

FPGA的配置电路JTAG链路

FPGA的JTAG电路通过串联电阻和外部上拉电阻后直连到Header2*7插座。信号说明如下表:

FPGAJTAG与Header之间的信号连接

XC7Z045-2FFG900I

Header2*7

信号名称

引脚号

电平

电源域

方向

引脚

说明

FP_TDI

TDI_0

LVCMOS

3.3V

I

10

转FPGA_JTAG_接口

FP_TDO

TDO_0

LVCMOS

3.3V

O

8

转FPGA_JTAG_接口

FP_TMS

TMS_0

LVCMOS

3.3V

I

4

转FPGA_JTAG_接口

FP_TCK

TCK_0

LVCMOS

3.3V

I

6

转FPGA_JTAG_接口

此外Header2*7的14PIN应该串联一个10K下拉电阻,作为JTAG_TRST信号。

配置non-dedicatedconfigurationI/Os

FPGAJTAGPL侧配置引脚处理

XC7Z045-2FFG900I

信号名称

引脚号

电平

电源域

方向

引脚

说明

PL_INIT_B

INIT_B_0

LVCMOS

3.3V

Bidirectio-nal(OD)

W9

通过4.7K电阻上拉至3.3V电源域。

ActiveLow,indicatesinitializationofconfigurationmemory.

PL_PRG_B

PROGRAM_B_0

LVCMOS

3.3V

I

Y9

通过4.7K电阻上拉至3.3V电源域。

ActiveLow,asynchronousresettoconfigurationlogic.

PL_CFGBVS

CFGBVS_0

LVCMOS

3.3V

I

V9

通过4.7K电阻上拉至3.3V电源域。

此管脚为bank0(bank14/15)电源域选择,如果bank0为2.5,则连接到VCCO_0,若电源域≤1.8V,则连接到GND。

PL_DONE_0

DONE_0

LVCMOS

3.3V

Bidirectio-nal

AA9

利用DONE信号输出高电平通过MOS管点LED灯指示用;同时MOS管D极输出的低电平送给MSP430作启动监测

ActiveHigh,DONEindicatessuccessfulcompletionof

configuration.

FPGA的启动配置FPGA从两片QSPIFLASHS25FL128SAGMFIR0上电启动,根据FPGABANK500的IO使用说明,如图5。下面将列出BOOT配置管脚和QSPI启动管脚的连接定义。

MIO-at-a-GlanceinBANK500

QSPIDUALSS8BitParallelI/O

FPGAPS配置信号处理

XC7Z045-2FFG900I

信号名称

引脚号

电平

电源域

方向

引脚

说明

PS_POR_B

D21

LVCMOS

3.3V

I

Poweronreset.由复位芯片MAX811提供复位电平,初始电平通过4.7K下拉到地,做兼容设计4.7K上拉到3.3V;复位芯片的输入由外部按键提供

FPGA_PS_33M333_CLK

A22

LVCMOS

3.3V

I

系统参考时钟,使用板上33.33MHz晶振提供

PS_MIO7

B24

LVCMOS

3.3V

I/O

20K下拉到地,为BANK0选择3.3V电压,包括MIOPIN0~15

PS_MIO8

C21

LVCMOS

3.3V

I/O

20K上拉到3.3V,为BANK1选择1.8V电压,包括MIOPIN16~53

PS_SRST_B

B19

LVCMOS

1.8V

I

连接到外部按键,低有效;同时,此信号可由MCU控制。Debugsystemreset,activeLow.

FPGAPS的BOOTModeMIO如下图6

BOOTModeMIOStrappingPins

根据图表信息,列出相关信号处理

FPGA上电启动配置信号处理

XC7Z045-2FFG900I

2S25FL256SAGMFIR01

信号名称

引脚号

电平

电源域

方向

引脚

说明

PS_MIO1

D23

LVCMOS

3.3V

I

7

串联0R电阻后接到QSPIFLSH片选管脚,低有效;需做4.7K上拉到3.3V

PS_MIO9

A24

LVCMOS

3.3V

I/O

16

串联0R电阻后接到接到QSPIFLSHSCK管脚

PS_MIO10

E22

LVCMOS

3.3V

I/O

15

串联0R电阻后接到接到QSPIFLSHSI管脚

PS_MIO11

A23

LVCMOS

3.3V

I/O

8

串联0R电阻后接到接到QSPIFLSHSO管脚

PS_MIO12

E21

LVCMOS

3.3V

I/O

9

串联0R电阻后接到接到QSPIFLSHWP管脚

PS_MIO13

F22

LVCMOS

3.3V

I/O

1

串联0R电阻后接到接到QSPIFLSHHOLD管脚

FPGA的存储接口定义系统运行存储在2片4GbDDR3MT41K256M16HA-125IT中,系统存储在2GBeMMCNANDFlashMTFC2GMDEA-0M。根据FPGA对PS侧的定义,我们可以规划出eMMC存储部分的定义、RGMII千兆网口的定义等。此部分将讲述eMMC和DDR3的信号定义

MIOBANK1PINs

FPGAeMMC存储接口信号处理

XC7Z045-2FFG900I

MTFC2GMDEA-0M

信号名称

引脚号

电平

电源域

方向

引脚

说明

PS_eMMC_RST_N

A19

LVCMOS

1.8V

I/O

K5

连接到eMMC的RST_N引脚,通过47K上拉到1.8VeMMC的电源,这样,用于存储信号的eMMC芯片不会复位

PS_eMMC_IO3

H18

LVCMOS

1.8V

I/O

B2

连接到eMMC的DATA3引脚,通过47K上拉到1.8VeMMC的电源

PS_eMMC_IO2

E20

LVCMOS

1.8V

I/O

A5

连接到eMMC的DATA2引脚,通过47K上拉到1.8VeMMC的电源

PS_eMMC_IO1

E18

LVCMOS

1.8V

I/O

A4

连接到eMMC的DATA1引脚,通过47K上拉到1.8VeMMC的电源

PS_eMMC_IO0

D20

LVCMOS

1.8V

I/O

A3

连接到eMMC的DATA0引脚,通过47K上拉到1.8VeMMC的电源

PS_eMMC_CMD

J18

LVCMOS

1.8V

I/O

M5

连接到eMMC的CMD引脚,通过10K上拉到1.8V电源域,推荐使用eMMC的电源

PS_eMMC_CLK

B20

LVCMOS

1.8V

I/O

M6

连接到eMMC的CLK引脚

注:eMMCMTFC2GMDEA-0MVCCQ使用磁珠电容滤波后的1.8V,VCC使用磁珠电容滤波后的3.3V;VSSQ与VSS同一接到GND;VDDIM引脚通过滤波电容接地。

FPGADDR3存储接口信号处理

XC7Z045-2FFG900I

2MT41K256M16HA共用

信号名称

引脚号

电平

电源域

方向

引脚

说明

PS_DDR3_CK_P

K25

SSTL15

1.5V

O

J7

连接到DDR3上CK脚

PS_DDR3_CK_N

J25

SSTL15

1.5V

O

K7

连接到DDR3上CK脚,通过40.2R端接电阻上拉到0.75VVTT电源

PS_DDR3_CKE

M22

SSTL15

1.5V

O

K9

连接到DDR3上CKE脚,通过40.2R端接电阻上拉到0.75VVTT电源

PS_DDR3_WE_N

N23

SSTL15

1.5V

O

L3

连接到DDR3上WE脚,通过40.2R端接电阻上拉到0.75VVTT电源

PS_DDR3_RAS_N

N24

SSTL15

1.5V

O

J3

连接到DDR3上RAS引脚,通过4.7K电阻上拉到1.5V,预留4.7K下拉到地

PS_DDR3_A0

L25

SSTL15

1.5V

O

N3

接到DDR3相应地址引脚,需加40.2R端接电阻上拉到0.75VVTT电源

PS_DDR3_A1

K26

SSTL15

1.5V

O

P7

接到DDR3相应地址引脚,需加40.2R端接电阻上拉到0.75VVTT电源

PS_DDR3_A2

L27

SSTL15

1.5V

O

P3

接到DDR3相应地址引脚,需加40.2R端接电阻上拉到0.75VVTT电源

PS_DDR3_A3

G25

SSTL15

1.5V

O

N2

接到DDR3相应地址引脚,需加40.2R端接电阻上拉到0.75VVTT电源

PS_DDR3_A4

J26

SSTL15

1.5V

O

P8

接到DDR3相应地址引脚,需加40.2R端接电阻上拉到0.75VVTT电源

PS_DDR3_A5

G24

SSTL15

1.5V

O

P2

接到DDR3相应地址引脚,需加40.2R端接电阻上拉到0.75VVTT电源

PS_DDR3_A6

H26

SSTL15

1.5V

O

R8

接到DDR3相应地址引脚,需加40.2R端接电阻上拉到0.75VVTT电源

PS_DDR3_A7

K22

SSTL15

1.5V

O

R2

接到DDR3相应地址引脚,需加40.2R端接电阻上拉到0.75VVTT电源

PS_DDR3_A8

F27

SSTL15

1.5V

O

T8

接到DDR3相应地址引脚,需加40.2R端接电阻上拉到0.75VVTT电源

PS_DDR3_A9

J23

SSTL15

1.5V

O

R3

接到DDR3相应地址引脚,需加40.2R端接电阻上拉到0.75VVTT电源

PS_DDR3_A10

G26

SSTL15

1.5V

O

L7

接到DDR3相应地址引脚,需加40.2R端接电阻上拉到0.75VVTT电源

PS_DDR3_A11

H24

SSTL15

1.5V

O

R7

接到DDR3相应地址引脚,需加40.2R端接电阻上拉到0.75VVTT电源

PS_DDR3_A12

K23

SSTL15

1.5V

O

N7

接到DDR3相应地址引脚,需加40.2R端接电阻上拉到0.75VVTT电源

PS_DDR3_A13

H23

SSTL15

1.5V

O

T3

接到DDR3相应地址引脚,需加40.2R端接电阻上拉到0.75VVTT电源

PS_DDR3_A14

J24

SSTL15

1.5V

O

T7

接到DDR3相应地址引脚,需加40.2R端接电阻上拉到0.75VVTT电源

XC7Z045-2FFG900I

1的DQL引脚

PS_DDR3_DQ1

A25

SSTL15

1.5V

I/O

F7

连接到DDR31的DQL引脚

PS_DDR3_DQ3

B27

SSTL15

1.5V

I/O

F8

连接到DDR31的DML引脚

PS_DDR3_DQS_P0

C27

SSTL15

1.5V

I/O

F3

连接到DDR31的DQSL1的DQL引脚

PS_DDR3_DQ5

B25

SSTL15

1.5V

I/O

H8

连接到DDR31的DQL引脚

PS_DDR3_DQ7

D26

SSTL15

1.5V

I/O

H7

连接到DDR31的DQU引脚

PS_DDR3_DQ9

A29

SSTL15

1.5V

I/O

C3

连接到DDR31的DQU引脚

PS_DDR3_DQ11

A30

SSTL15

1.5V

I/O

C2

连接到DDR31的DMU引脚

PS_DDR3_DQS_P1

B30

SSTL15

1.5V

I/O

C7

连接到DDR31的DQSU1的DQU引脚

PS_DDR3_DQ13

C28

SSTL15

1.5V

I/O

A2

连接到DDR31的DQU引脚

PS_DDR3_DQ15

D28

SSTL15

1.5V

I/O

A3

连接到DDR32MT41K256M16HA

信号名称

引脚号

电平

电源域

方向

引脚

说明

PS_DDR3_DQ16

H27

SSTL15

1.5V

I/O

E3

连接到DDR32的DQL引脚

PS_DDR3_DQ18

H28

SSTL15

1.5V

I/O

F2

连接到DDR32的DQL引脚

PS_DDR3_DM2

H29

SSTL15

1.5V

O

E7

连接到DDR32的DQSL引脚

PS_DDR3_DQS_N2

F29

SSTL15

1.5V

I/O

G3

连接到DDR3引脚

PS_DDR3_DQ20

E30

SSTL15

1.5V

I/O

H3

连接到DDR32的DQL引脚

PS_DDR3_DQ22

G30

SSTL15

1.5V

I/O

G2

连接到DDR32的DQL引脚

PS_DDR3_DQ24

J29

SSTL15

1.5V

I/O

D7

连接到DDR32的DQU引脚

PS_DDR3_DQ26

J30

SSTL15

1.5V

I/O

C8

连接到DDR32的DQU引脚

PS_DDR3_DM3

K28

SSTL15

1.5V

O

D3

连接到DDR32的DQSU引脚

PS_DDR3_DQS_N3

L29

SSTL15

1.5V

I/O

B7

连接到DDR3引脚

PS_DDR3_DQ28

K30

SSTL15

1.5V

I/O

A7

连接到DDR32的DQU引脚

PS_DDR3_DQ30

L30

SSTL15

1.5V

I/O

B8

连接到DDR32的DQU引脚

PS_DDR_VRP_502

M21

N/A

N/A

N/A

VRP通过80.6R下拉到GND

PS_DDR_VRN_502

N21

N/A

N/A

N/A

VRN通过80.6R上拉拉到

注1:DDR3ZQ引脚需要接240R电阻到地;

注2:DDR3的电源及滤波电容在电源模块进行描述

FPGAPS侧其他接口电路PS侧有两路LED灯使用方式如下

FPGAPS侧指示信号处理

XC7Z045-2FFG900I

信号名称

引脚号

电平

电源域

方向

引脚

说明

PS_LED_G

F19

LVCMOS

1.8V

I/O

通过N-MOSAO3400点亮板上0603的绿色SMDLED

PS_LED_R

C19

LVCMOS

1.8

I/O

通过N-MOSAO3400点亮板上LED571-0112F的红灯,此LED用于面板指示

FPGAPS侧将引出一路UART信号到MAX3232芯片输出一路RS232信号,此MAX3232的另一个通道,由PL侧的UART信号提供转换源,具体芯片使用见PL侧信号定义相关部分

FPGAPS侧RS232信号处理

XC7Z045-2FFG900I

MAX3232ESE+

信号名称

引脚号

电平

电源域

方向

引脚

说明

PS_MIO14

B22

LVCMOS

3.3V

I/O

12

串联0R电阻后接到Logicdataoutput(toUART)

PS_MIO15

C22

LVCMOS

3.3V

I/O

11

串联0R电阻后接到Logicdatainput(fromUART)

由于FPGAPS侧管脚数量有限,PS侧所需的RS422等信号,使用EMIOInterface挂到PL侧引出,内部使用AXI总线相连接。这部分在PL侧相关单元描述

FPGA与FIBER接口电路本系统单板板载两颗HTS1302-LH-001XX光模块。该模块是一款低功耗、高性能的单路光收发、双LC口双纤双向光收发一体模块。传输距离1km速率为10.3125Gbps,发射中心波长1310nm。3.3V直流供电,工业级温度。发射部分信号引脚(TD+和TD-)接口采用交流CML电平。模块还具有发送信号关断控制功能。

传输信号典型应用图

根据HTS1302-LH-001XX的管脚定义,使用GTXBANK110作为收发信号,3.3V电源域的HRBANK10作为控制信号连接脚。下表将详细定义FPGA与FIBER的连接:

FPGA与HTS1302-LH-001XX信号处理

XC7Z045-2FFG900I

HTS1302-LH-0011

信号名称

引脚号

电平

电源域

方向

引脚

说明

FPGA_FIBER1_TX_P

AH2

CML

AC-COUPLE

O

1

连接到光模块发射端输入正,由于两端都为CML电平,不需要匹配

FPGA_FIBER1_TX_N

AH1

CML

AC-COUPLE

O

3

连接到光模块发射端输入负,由于两端都为CML电平,不需要匹配

FPGA_FIBER1_RX_P

AH6

CML

AC-COUPLE

I

7

连接到光模块接收端输入正,由于两端都为CML电平,不需要匹配

FPGA_FIBER1_RX_N

AH5

CML

AC-COUPLE

I

9

连接到光模块接收端输入负,由于两端都为CML电平,不需要匹配

FPGA_FIBER1_LOS_N

AK15

LVCMOS

3.3V

I/O

5

连接到光模块LOS引脚,此引脚LVTTL电平输出。引脚输出低电平时,表示光信号正常;引脚输出高电平时,表示光信号异常。模块内部已上拉。

FIBER1_TDIS_N

AG15

LVCMOS

3.3V

I/O

6

连接到发射端使能控制脚,此引脚为LVTTL电平,低有效,同时通过4.7K电阻上拉到3.3V

XC7Z045-2FFG900I

信号名称

引脚号

电平

电源域

方向

引脚

说明

CLK_FIBER_P

AA8

CML

AC-COUPLE

I

通过串联100nF的耦合电容连接到125M差分晶体的输出P端;差分晶体输出端需预留150R的对地匹配电阻;FPGA接收端,P端与N端之间应预留100R端接电阻

CLK_FIBER_N

AA7

CML

AC-COUPLE

I

通过串联100nF的耦合电容连接到125M差分晶体的输出N端;差分晶体输出端需预留150R的对地匹配电阻

光模块电源外围滤波电路参考下图:

参考外围滤波电路

FPGAGigabitEthernet接口电路GEB接口采用三片88E1512与FPGA处理器XC7Z045-2FFG900I相连接,高速数据接口为RGMII接口,其余控制接口为LVCMOS18电平。其中两片88E1512加载在PS侧,一片加载在PL侧。以太网模块的对外接口为HJ303J-36ZKW高速连接器,该连接器传差分信号的是超五类网线芯线。板上MDIO信号后端接1:1变压器后送至连接器。以太网单元的实现方式如下图。

以太网模块的硬件拓扑

88E1512是的10M/100M/1000M以太网收发器,兼容协议。该芯片内部集成了RGMII/SGMII接口。88E1512使用方式灵活,支持RGMIItoCopper、SGMIItoCopper/Fiber/SGMII以及CoppertoFiber模式。88E1512支持MDI/MDIX自协商模式,其详细框图如下:

88E1512的系统架构

88E1512的RGMII接口与FPGA处理器XC7Z045-2FFG900I的MAC接口相连接,RGMII信号为HSTL_I_18电平。88E1512的SerDes输入输出接口采用CML逻辑电路产生,芯片内部含有Bias电平与端接电阻,设计中不需要进行外部端接匹配。88E1512与XC7Z045-2FFG900I之间采用直连。下图为RGMII之间的连接示意图。

RGMII的连接

FPGA与PHY芯片之间用MDIO总线通讯,MDIO接口包括两根信号线:MDC和MDIO,通过它,MAC层芯片(或其它控制芯片)可以访问物理层芯片的寄存器,并通过这些寄存器来对物理层芯片进行控制和管理。XC7Z045-2FFG900I的MDIO总线为1.8VLVCMOS,因此这里设计上要求88E1512的VDDO电源使用1.8V供电。依据可靠性要求,每片PHY单独使用一片25MHz晶体作为时钟源,输出的MDIO信号经HX5084NL1:1变压器送给HJ30J连接器。其ACT、LINK灯信号在板上驱动N-MOSAO3400点LED灯,MOS管D极信号还需送到HJ30J连接器,方便机箱网口点灯。

下图是PS侧管脚MIO管脚分配,根据此图88E1512的引脚对外接口的说明如下。

MIOBANK1PINs

FPGAPS侧RGMII信号处理

XC7Z045-2FFG900I

88E1512共用

信号名称

引脚号

电平

电源域

方向

引脚

说明

PS_PHY_MDIO

C18

LVCMOS

1.8V

I/O

8

接到PS侧两个PHY芯片的MDIO引脚,同时使用4.7K电阻上拉到1.8V

PS_PHY_Z_MDC

D19

LVCMOS

1.8V

I/O

7

串联33R电阻后的信号接到两个PHY芯片的MDC引脚,同时使用4.7K电阻上拉到1.8V

XC7Z045-2FFG900I

88E15121

信号名称

引脚号

电平

电源域

方向

引脚

说明

PS_PHY1_RST_N

F20

LVCMOS

1.8V

I/O

16

接到PHY芯片RESET_N脚,同时使用4.7K电阻下拉到GND

PHY1_TX_CLK

L17

LVCMOS

1.8V

I/O

53

串联33R电阻后接到PHY相应管脚

PS_PHY1_TXD0

H22

HSTL_I_18

1.8V

I/O

50

连接到PHY芯片相应管脚

PS_PHY1_TXD1

L18

HSTL_I_18

1.8V

I/O

51

连接到PHY芯片相应管脚

PS_PHY1_TXD2

H21

HSTL_I_18

1.8V

I/O

54

连接到PHY芯片相应管脚

PS_PHY1_TXD3

K17

HSTL_I_18

1.8V

I/O

55

连接到PHY芯片相应管脚

PS_PHY1_TX_CTRL

G22

LVCMOS

1.8V

I/O

53

连接到PHY芯片相应管脚,同时通过4.7K上拉到1.8V电源域

PS_PHY1_RX_CLK

K18

LVCMOS

1.8V

I/O

46

接到PHY芯片相应管脚,注意在PHY芯片端串联33R电阻

PS_PHY1_RXD0

G21

HSTL_I_18

1.8V

I/O

44

连接到PHY芯片相应管脚

PS_PHY1_RXD1

H17

HSTL_I_18

1.8V

I/O

45

连接到PHY芯片相应管脚

PS_PHY1_RXD2

B21

HSTL_I_18

1.8V

I/O

47

连接到PHY芯片相应管脚

PS_PHY1_RXD3

A20

HSTL_I_18

1.8V

I/O

48

连接到PHY芯片相应管脚

PS_PHY1_RX_CTRL

F18

LVCMOS

1.8V

I/O

43

连接到PHY芯片相应管脚,同时通过4.7K上拉到1.8V电源域

FPGAPL侧RGMII信号处理

XC7Z045-2FFG900I

88E1512#2

信号名称

引脚号

电平

电源域

方向

引脚

说明

PL_PHY2_RST_N

J4

LVCMOS

1.8V

I/O

16

接到PHY芯片RESET_N脚,同时使用4.7K电阻下拉到GND

PL_PHY2_TXD_CLK

D15

LVCMOS

1.8V

I/O

53

串联33R电阻后接到PHY相应管脚

PL_PHY2_TXD0

C14

HSTL_I_18

1.8V

I/O

50

连接到PHY芯片相应管脚

PL_PHY2_TXD1

C13

HSTL_I_18

1.8V

I/O

51

连接到PHY芯片相应管脚

PL_PHY2_TXD2

C12

HSTL_I_18

1.8V

I/O

54

连接到PHY芯片相应管脚

PL_PHY2_TXD3

B12

HSTL_I_18

1.8V

I/O

55

连接到PHY芯片相应管脚

PL_PHY2_TXD_CTRL

B14

LVCMOS

1.8V

I/O

53

连接到PHY芯片相应管脚,同时通过4.7K上拉到1.8V电源域

PL_PHY2_RXD_CLK

E13

LVCMOS

1.8V

I/O

46

接到PHY芯片相应管脚,注意在PHY芯片端串联33R电阻

PL_PHY2_RXD0

G21

HSTL_I_18

1.8V

I/O

44

连接到PHY芯片相应管脚

PL_PHY2_RXD1

H17

HSTL_I_18

1.8V

I/O

45

连接到PHY芯片相应管脚

PL_PHY2_RXD2

B21

HSTL_I_18

1.8V

I/O

47

连接到PHY芯片相应管脚

PL_PHY2_RXD3

A20

HSTL_I_18

1.8V

I/O

48

连接到PHY芯片相应管脚

PL_PHY2_RXD_CTRL

F18

LVCMOS

1.8V

I/O

43

连接到PHY芯片相应管脚,同时通过4.7K上拉到1.8V电源域

PL_PHY2_MDC

J3

LVCMOS

1.8V

I/O

7

接到PL侧PHY芯片的MDIO引脚,同时使用4.7K电阻上拉到1.8V

PL_PHY2_MDIO

L1

LVCMOS

1.8V

I/O

8

串联33R电阻后的信号接到PL侧PHY芯片的MDC引脚,同时使用4.7K电阻上拉到1.8V

88E1512基本电路的设计

引脚名称

引脚号

电平

电源域

方向

电路连接说明

LED2/INT

12

--

1.8V

O,D

NC

CONFIG

15

LVCMOS

1.8V

I

用于设定PHYAD[0]的地址,下拉时PHYAD[0]=0,上拉时PHYAD[0]=1。设计中PL使用10K电阻上拉到VDDO,同时预留下拉到地电路。PS侧两颗PHY芯片一颗PHYAD[0]=1,另一颗PHYAD[0]=0

CLK125

9

LVCMOS

1.8V

O

125MHz时钟输出,连接到TP点用作电路调试。

XTAL_IN

34

LVCMOS

1.8V

I

时钟输入,支持Crystal和Oscillator两种时钟,用作PHY芯片的工作时钟。本设计中时钟25MHzOscillator时钟,

XTAL_OUT

33

LVCMOS

1.8V

O

工作时钟使用Crystal时,作为时钟输出使用,本设计中时钟Oscillator作为工作时钟,该引脚悬空。

RSET

30

NC

NC

I

内部偏置参考电阻,使用4.99K1%电阻下拉到地。

HSDACN/P

31/32

Analog

NC

O

NC

TSTP

29

O

NC

88E1512的电源、地信号的处理

引脚名称

引脚号

电路连接说明

AVDDC18

35

1.8V模拟电源输出,设计中使用磁珠滤波,每个电源引脚附近摆放电容0.1uF电容,除此之外,由于PHY芯片使用的1.8V为内部DC-DC电源转出,应再放置一些滤波电容,且电容容值不可太小,应介于22uF-47uF。

AVDD18

3/19/26/38

AVDD33

20/25

3.3V模拟电源输入,设计中使用磁珠滤波,每个电源引脚附近摆放一颗0.1uF电容。

REG_IN

36

内部电源转化器电源输入引脚3.3V。88E1512内部包含两个电压转换器,分别输出1.8V和1.0V电压,提供AVDD和DVDD使用。设计中可以根据需选择使用内部电压转换器或外部提供电源。当使用外部电源供电时,该引脚悬空。

本设计使用内部电压转换器提供1.8V和1.0V电源,设计中需要为该引脚提供4.7uF以上的滤波电容。

注意:

使用外部电源供电时,REG_IN/AVDD18_OUT/DVDD_OUT/

REGCAP1/REGCAP2必须悬空,否则可能导致芯片损坏。

若使用内部电源变换器供电时,AVDD和DVDD必须同时使用内部电源,不支持外部电源和内部电源混合使用的模式。

REGCAP1/2

37/41

内部电源变换器外接电容引脚,当使用内部电源转换时,在两个引脚之间连接一个220nF±10%电容,并靠近芯片放置。当使用外部电源供电时,这两个引脚必须悬空。设计使用内部电源转换器。

AVDD18_OUT

39

内部电源转换器1.8V输出,给AVDD18和AVDDC18供电。当使用外部电源供电时,该引脚必须悬空,注意事项见REG_IN。本设计使用内部电源供电。

DVDD_OUT

40

内部电源转换器1.0V输出,给DVDD供电。当使用外部电源供电时,该引脚必须悬空,注意事项见REG_IN。本设计使用内部电源供电。

VDDO

11/49/52

3.3V/2.5V/1.8VIO电源,供电电压使用VDDO_SEL选择。本设计中使用1.8V,VDDO使用内部电源转换器输出的1.8V提供。

VDDO_SEL

10

当VDDO为3.3V/2.5V时,VDDO_SEL接地;当VDDO为1.8V时,VDDO_SEL接VDDO。本设计中VDDO使用1.8V。

DVDD

6/42

1.0V数字电源输入,要求滤波电容不低于4.7uF。

VSS

EPAD

GND

FPGA与ADC/DAC接口电路此部分参见3.2节

FPGA的GPIO接口电路FPGA的GPIO主要有以下几种用途:单板共预留24个GPIO口,16个GPI口用于外部开关的输入,16个GPIO口用于LCD,以及6个GPO口预留给外部的LED灯。这些信号通过板上电平转换芯片TXS0108ERGYR做隔离保护送入板上连接器。

TI公司的电平转换芯片TXS0108ERGYR为20PinVQFN封装,4.5尺寸。该芯片支持8bit双向电平转换,无需方向控制,具有输出使能控制功能,能够保证上电期间输出信号为高阻态,满足FPGA的IO口上电期间对于输入引脚的状态要求。TXS0108E的电平转换支持推挽模式与开漏模式两种形式,推挽模式的最大速率为110Mbps,开漏模式的最大速率为1.2Mbps。根据TXS0108ERGYR芯片手册,我们选用A端连接板上芯片,B端连接出板的连接器。

应用中需要将TXS0108ERGYR的OE引脚配置1K下拉,以确保上电器件输出信号为高阻态。OE的电平参考VCCA的电源电压,设计中需连接到VCCA。TXS0108E拥有两组不同的电源输入VCCA、VCCB,使用中需要保证VCCA≦VCCB芯片才能正常工作。TXS0108ERGYR的IO口支持双向数据传输,对于多余的IO端口,要求下拉到GND处理。原理图可参考下图:

TXS0108参考原理图

24个预留GPIO的处理

24个预留的GPIO应使用3.3V电源域的HRBANK的管脚。信号每8个为一组,共需3片TXS0108ERGYR隔离保护。TXS0108另一端信号连接到J30J-51-ZKW连接器。注意,TXS0108两端信号都需要预留DNP_4.7K电阻上拉到对应的3.3V电源域。

16个按键GPIO的处理

16个预留的SW_GPIO应使用3.3V电源域的HRBANK的管脚。信号每8个为一组,共需2片TXS0108ERGYR隔离保护。TXS0108另一端信号连接到J30J1-37ZKW-J连接器。注意,TXS0108两端信号都需要预留DNP_4.7K电阻上拉到对应的3.3V电源域。

16个LCDGPIO的处理

本板需做机箱上LCD显示屏的驱动和显示。依据客户需求,显示屏选用的是维信诺V0064-CA-010_module;LCD与FPGA的通信可以选择4线SPI、3线SPI、8-bit8080并口和8-bit6800并口四种方式,为方便客户使用,将模块所需的16根信号线全部引出到板上J30J连接器。16个LCD信号应使用3.3V电源域的HRBANK的管脚。

信号每8个为一组,共需2片TXS0108ERGYR隔离保护。TXS0108另一端信号连接到J30J1-37ZKW-J连接器。注意,TXS0108两端信号都需要预留DNP_4.7K电阻上拉到对应的3.3V电源域。

6个LED的处理

本板上需要从FPGA端引出6个LED控制信号,MSP430F5438A端引出2个LED控制信号,经MOS管处理后送入J30J连接器。处理后的信号给J30J可以直接用于点灯。6个预留的LED信号应使用3.3V电源域的HRBANK的管脚。可参考下方原理图:

LED部分参考原理图

PL侧其他通信接口电路本系统需要4路RS-422信号,1路RS-232信号通过J30J连接器与板外通信。1路RS-232信号用于板上调试。其中用于板上调试的RS-232由PL侧的信号引出,PS侧的RS-232送到J30J连接器,由于PS侧接口有限,PS侧的信号通过内部AXI总线挂到PL侧端口引出。4路RS-422信号3路由PL侧引出,1路由PS侧控制,由于PS侧接口有限,PS侧的信号通过内部AXI总线挂到PL侧端口引出。

RS232信号由MAX3232ESE+RS-232收发器芯片转出。MAX3232ESE+是使用3.3V至5V的一个低功耗的真RS-232收发器,在正常工作模式下可确保250Kbps的数据速率,MegaBaud工作模式下保证1Mbps的速率。MAX3232ESE+具有两路接收器和2路驱动器,外部仅需四个0.1uF的外部小尺寸电荷泵电容。设计时需要注意,在信号与J30J连接器端请使用合适的TVS管保护输入输出信号。信号应使用3.3V电源域的HRBANK的管脚。其电路可参考下图:

RS232部分参考原理图

RS-422信号由MAX3491AEASD+RS-422收发器芯片转出。MAX3491是一款3.3V工作电压低功耗收发器。用于RS-422和RS-485等串行数据接口标准系统中,内部有驱动、接收和使能控制模块。可实现全双工传输。最大传输速率为10Mbps。MAX3491主要是与外部串行接口进行数据的传输,在使能端的控制下它将外部的逻辑信号通过驱动器转化为差分信号,也可以由接收器中的比较器将接收的差分信号耦合到比较器的输入端,利用比较器将差分信号转换为单端的逻辑电平信号。其数据引脚不支持输入悬空。当使能端同时不使能的时候,芯片将进入一个低功耗的关断模式。设计时需要注意,在信号与J30J连接器端请使用合适的TVS管保护输入输出信号。信号应使用3.3V电源域的HRBANK的管脚。其原理图可参考下图:

RS422部分参考原理图

未使用管脚处理GTXBANK中仅使用110BANK其余109111112BANK没有使用。这些BANK的差分接收管脚都应当通过串联1uF电容接地。其中112BANK上的MGTAVTTRCAL和MGTRREF管脚应做如下图处理,PCB布线时也应注意等长:

MGTAVTTRCAL和MGTRREF管脚参考图

其余BANK9为空余BANK,连接VCC3V3电源域,IO管脚悬空不连接;

其他BANK上的未使用管脚在原理图中放置placenoconnect

AD/DA模拟信号处理单元本单元框图如下:

单板模拟单元框图

其中,模拟模块的时钟框图如下所示:

模拟单元时钟框图

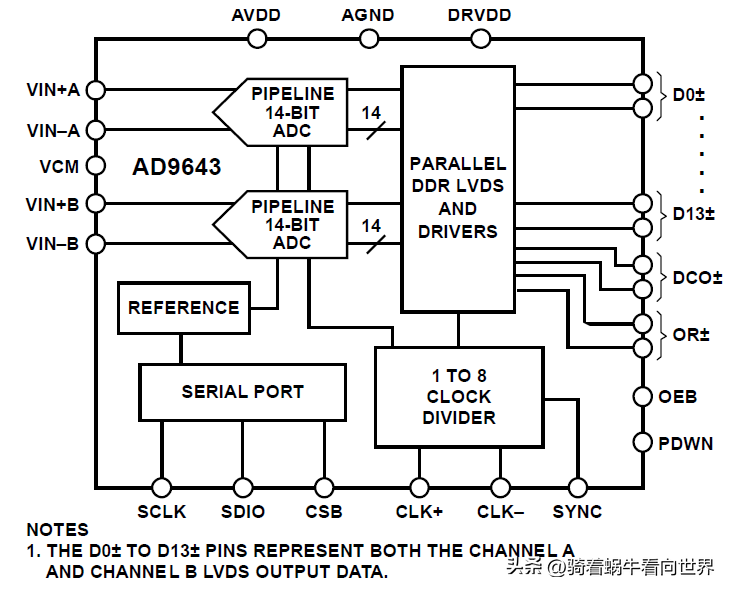

ADC模块ADC芯片采用ADI公司的AD9643-250,它是一款14位、170/210/250MSPS的1.8V的双通道ADC。可达到的指标有SNR:70.6dBFS;SFDR:83dBc@185MHz;采样率:170MHz;模拟信号输入幅值:1.4Vpp~2.0Vpp;通道隔离度:95dB;DNL:±0.75LSB;INL:±1.5LSB;ENOB:11.3Bits@185MHz能够满足客户需求

芯片系统框图如下:

AD9643框图

DAC模块DA的速率和频率要求都较高,依据实际的项目指标要求,选择的型号为ADI公司的AD9739,它是一款14位,2500MSPS的RF数模转换芯片。可以达到的主要指标有:最大2.5GHz的采样率;2通道的LVDSDDR通道,最大到1.25GSPS/通道;可编程输出电流:8.7mA~31.7mA;INL:±1.3LSB;DNL:±0.8LSB;输出幅值:±1.0V

芯片框图如下:

AD9739框图

AD9739的设计请参考ADI官方设计文档《AD9739-R2-EBZRevABSchematic》、《AD9739-MIX-EBZRevASchematic》。DAC的工作时钟由是外部SSMA的输入信号经巴伦转换后输入,也可由ADCLK914芯片整形后输入。其SPI通信接口,控制、状态接口均接到电源域的HRBANK。其中CS、SCLK、MISO、MOSI、信号应使用4.7K电阻上拉到3.3V电源域,IRQ应使用10K电阻上拉到3.3V电源域,RESET除了4.7K上拉到3.3V还应预留10K接地。其DCO、DCI信号要接到FPGAHPBANK的MRCC管脚。FPGA送给DAC的信号为LVDS电平,此处应使用FPGA的HPBANK管脚。输出的差分电流信号IOUT经过巴伦TC1-1TG2+差分转单端后将输出信号送给SSMA

其他模块依据前文所述,AD9739的输入时钟由外部SSMA输入。SSMA输入的时钟经巴伦RFT4042G-1/1单端转差分后送给AD9739的DACCLK_P/N管脚,此时钟最大可达1.6GHz。为保证性能指标,线板上将单转差的巴伦作为预留电路,SSMA输入时钟经由ADCLK914BCPZ-WP芯片完成单端转差分的功能,送给AD9739。

ADCLK914BCPZ-WP是一款高速OC门输出的HVDS时钟Buffer芯片,适用于模拟信号。其转换速率可达7.5GHz,传播延时160ps,随机抖动约110fs。芯片功能框图如下:

ADCLK914功能框图

AD9643的输入时钟55Mhz也由外部SSMA输入。SSMA输入的时钟经巴伦RFT4042G-1/1单端转差分后送给AD9643的CLK_P/N。为保证性能指标,板上AD9643的时钟信号可以由巴伦直接输出,也可将巴伦的输出时钟经时钟芯片AD9518-0整形后送给板上AD9643。为调试方便AD9518-0芯片的时钟源由板上预留的100MHz差分时钟晶振提供。

AD9518-0是一款6路输出的时钟发生器,集成2.8GHz的内部VCO。板上通过SSMA输入55MHz时钟源,或者100MHz差分晶振来提供输入。芯片可与FPGA通过SPI进行通信。6路输出板上仅使用一路,接到FPGAHPBANK的MRCC管脚,其余输出接100nF交流耦合电容后放置TP点用于测试。6路输出都需要预留200R的对地电阻。

芯片的控制、状态和SPI通信管脚应根据相应的电平,连接到FPGA对应电平的HRBANK管脚上。电源应按照参考设计推荐值进行滤波处理。其功能框图如下:

AD9518-0功能框图

监控单元监控单元使用一片MSP430F5438A作为控制MCU,提供电源检测、电流检测、复位、温度监控,以及实现与系统FPGA间的低速通信。监控单元的详细架构如下图:

监控单元的详细架构

监控单元作为单板的系统管理模块,分别与FPGA信号处理单元、电源单元,接口单元存在电气连接。

MSP430F5438A是一款集成14通道12bit模数转换器的超低功耗微控制器,工作电压1.8~3.6V,具有256Kb路内置Flash与16Kb内置SRAM,支持最多4路SPI接口与4路I2C接口,支持最高工作时钟25MHz。MSP430F5438A最多包含87个GPIO引脚,支持LVTTL输入与LVCMOS输出,所有GPIO引脚都可以根据需要选择内部上下拉。

MSP430F5438A支持内部时钟与外部时钟模式,内部时钟支持10KHzVLOCLK,32.768KHzREFOCLK与DCOCLK三种时钟方式。外部时钟XT1支持低功耗时钟32.768KHz,与高速时钟4MHz~25MHz输入。外部时钟XT2支持4MHz~25MHz工作范围。MSP4305438A的详细框图如下:

MSP430F5438A的详细框图

下面将介绍与MSP430F5438A相连的电路。

电压电流检测电压电流监控部分如下图所示:

PowerDetect

温度检测MSP430F5438A的温度检测功能配合温度传感器DS18B20实现。本设计中共使用3片DS18B20芯片,设计中使用一颗DS18B20实现对FPGA周围温度的检测,一颗放置在电源芯片周围,实现对大功耗电源芯片温度的监测,还有一颗放置在AD9379芯片附近,监测AD/DA模拟部分的温度。

DS18B20是一颗单片可编程1-Wire数字温度计,每颗芯片具有一个唯一的64bitdeviceID,设计中可以将多颗DS18B20连接到一个控制器的引脚上完成数据传输。DS18B20使用3.3V_AUX供电,与单片机之间的连接关系如下图,Vpu与VDD采用相同电源:

DS18B20的电路连接

看门狗复位MSP430F5438A将与MAX706TESA,FPGA配合完成硬件看门狗功能。MAX706的功能框图如下图所示:

MAX706功能框图

MAX706主要用于电源监控和看门狗,本系统中没有使用电源监控功能,将PFI引脚电平置为3.3V分压后得到的1.8V。

WDI,是看门狗计数器输入引脚,此引脚连接到FPGA的IO上,看门狗芯片不会去统计FPGA输出的脉冲数,而是只检测在这个引脚上是否发生了电平翻转,FPGA需要不停地控制这个引脚翻转,看门狗定时器的周期是1.6s,如果在这1.6s内没检测到电平翻转,那么说明FPGA跑飞了,此时就会在RST引脚上输出一个200ms的低电平告知MSP430F5438A,MSP430F5438A则通过与FPGA相连的复位信号FPGA_MCU_RST控制FPGA程序的复位。注意复位信号需要串电阻后连接。

此部分原理可参考下图:

MAX706参考原理图

FPGA通信监测FPGA与MSP430F5438A预留有一个IIC低速数据通信接口,两个IO口。同时FPGA的复位信号会与MSP430F5438A相连接,MSP430F5438A可通过此管脚控制FPGA的复位。FPGA的DONE信号也与MCU相连,当上电程序加载完成后,DONE信号经过MOS管点灯,同时将MOS管D极低有效信号送给MCU,当MCU监测到此信号,则认为FPGA启动成功。FPGA与MSP430F5438A的IIC通信中,MSP430是作为主机,FPGA作为从机

MCU最小系统MSP430F5438A的最小工作系统设计包含电源电路,时钟电路,调试电路复位电路四个部分,具体的信号描述参考MSP430F5438A的引脚分配表中的INNER部分。一下几点设计中需要注意:

MSP430F5438A的工作电压选用3.3V,使用LTM4644提供的3.3V_MCU作为电压源。MSP430F5438A的数字电源、模拟电源供电注意滤波,滤波要求如下图:

MSP430F5438A的模拟电源滤波

系统时钟选择8MHzCRYSTAL作为时钟源。复位电路集成RC上电复位和外部按键复位,可参考下方原理图:

MCU复位及时钟参考原理图

电源单元电源单元用于给单板上各芯片提供电源,且满足板上各电源的上掉电时序要求。为了方便单板调试,单板设计只需要1个电源:5V或者12V。5V电源由CPCI底板通过PCI连接器J1输入给本板。12V的VIN电源使用标准ATX电源12V通过J30J-9ZKW-J送到板上。所以板上电源单元的设计兼容5V与12V的输入。根据功耗评估表,设计具体电源框图如下:

单板电源框图

关键芯片工作原理简介LTM4628

LTM4628是凌特公司的电源模块,内部集成MOS管和变压器,可以方便的节省板子面积。4.5~26.5V宽电压输入,可提供两路8A或者一路16A输出电源,输出电压范围0.6V~5.5V。尺寸有15和15两种,带有集成型頂面散熱器。提供5V内部电压输出,其简化内部框图如下。

LTM4628EV简化框图

典型应用图如下:

双通道输出

单通道输出

LTM4644

LTM4644是凌特公司的电源模块,内部集成功率MOS管和电感,只需要提供少量外部电容,提供4路4A输出(输出可并联),输出电压0.6V~5.5V,输入电压范围4~14V,封装9mm×15mm×5.01mmBGA,提供内部4路3.3V电压输出INTVCC1/2/3/4.其简化框图如下:

LTM4644简化框图

典型应用图如下:

LTM4644参考原理图

TPS74401

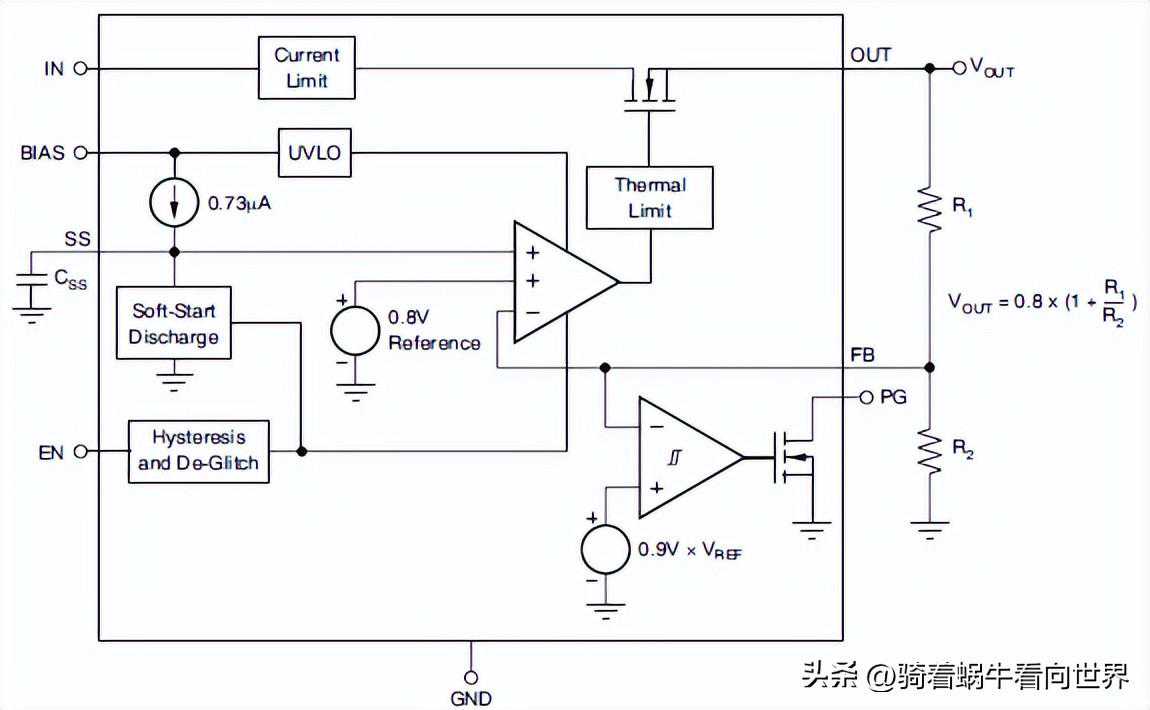

TPS74401是一款3A输出的LDO电源芯片,可调输出电压0.8V~3.6V。封装5mm*5mm*1mm的QFN封装,适用于FPGA和DSP的电源。

TPS74401简要原理框图

TPS51200

TPS51200是专用于DDR的端接电源VTT,能够提供2A的VTT电流输出,且可以提供10mA的VTTREF输出。封装VSON(10):3x3mm。输入电压:3.3V或者2.5V,VLDOIN:1.1~3.5V,工作温度范围:-40°~+85°,

TPS51200简要原理框图

TPS51200典型应用

REF3012

REF3012是一款固定输出1.25V的高精度低功耗温漂小的LDO电源芯片

最大输出电流25mA,精度为0.2%。封装为SOT-23-3。

REF3012简要原理框图

REF3012典型应用

SGM2032-ADJ

SGM2032-ADJ是一款可调输出的高精度低功耗温漂小的LDO电源芯片

可调输出范围0.8V到5V。封装为SOT-23-5。

SGM2032-ADJ典型应用

上电掉电时序控制依据FPGA对时序的要求,以及不同电源的电流大小,上电时序框图如下:

单板上电时序框图

上电时序通过控制电源芯片的EN脚实现时序控制,所有时序都是通过PG+RC延时控制EN脚实现。掉电时序和上电时序相反。当所有电源上电都完成后,使用电源芯片的PowerGood信号点亮一颗板载LED灯,作为上电完成的指示,其电路可参考如下原理图:

AllPowerGood参考原理图

电压检测板上需要监控的输出电源都连接到MSP430的ADC做电压检测。共监控8路ADC。当有电源出现严重问题时,MSP430需要把POR_N拉低,防止过电流。

电流检测由于面积限制,电流检测只做总输入电源VIN的电流检测。通过高侧单极分流检测计INA168检测输入电阻两端的电压实现电流检测。INA168放大5mΩRs电阻两端的电压并输入到MSP430的ADC,MSP430计算出电流,实现电流检测。需要2路MSP430的ADC。

INA168的电路应用

温度检测LTM4628和LTM4644都有内部温度检测二极管输出,dVD/dT通常为–2mV/°C,外接ADC可以检测温度。根据上文中提到的,PCB布局时会放置一颗DS18B20在电源芯片附近以便监测温度

电路连接根据输入电源简单化原则,本板需要一个主电源(12V或者5V),主电源通过保险丝跳选,保险丝后端VIN应接TVS管作为保护,之后连接EMI滤波器BNX028-01L,防止外部电源干扰板上敏感信号。经过EMI滤波器的电源将经过5mΩ级别的电阻,此电阻用于检测输入电流。

输入电源VIN在板上产生板上所有电源。具体见上图:单元电源结构框图。DC-DC电源都是选择的电源模块应用也比较简单,只需外部少量的些电阻电容即可。

Vout=0.6V*(1+60.4K/RFB)=0.6V*(1+60.4K/86.6K)=1.018V其他电阻电容参数参考下图:

LTM4620阻容参数选择

FPGA的3.3V和1.8V也是使用LTM4628,两通道独立输出。计算公式如下:

Vout=0.6V*(1+60.4K/RFB)=0.6V*(1+60.4K/13K)=3.387V

Vout=0.6V*(1+60.4K/RFB)=0.6V*(1+60.4K/30.1K)=1.803V

Vout=0.6*(60.4+Rfb)/Rfb=0.6*(60.4+13.24)/13.24=3.337V

Vout=0.6*(60.4+Rfb)/Rfb=0.6*(60.4+21.83)/21.83=2.260V

Vout=0.6*(60.4+Rfb)/Rfb=0.6*(60.4+39.2)/39.2=1.524V

Vout=0.6*(60.4+Rfb)/Rfb=0.6*(60.4+8.06)/8.06=5.090V

LTM4644Rfb阻值选择

TPS74401Rfb阻值选择

考虑实际走线中的线路压降,除ADC、DAC电源之外。初始电阻值皆上调2%。计算公式如下:

Vout=0.8V*(1+R1/R2)=0.8V*(1+2.67K/10K)=1.013V(VCC1V0_MGTAVCC)

Vout=0.8V*(1+R1/R2)=0.8V*(1+1K/2K)=1.2V(VCC1V2_MGTAVTT)

Vout=0.8V*(1+R1/R2)=0.8V*(1+1.29K/1K)=1.832V(VCC1V8_MGTVCCAUX)

Vout=0.8V*(1+R1/R2)=0.8V*(1+1.24K/1K)=1.792V(VCC1V8_ADC)

Vout=0.8V*(1+R1/R2)=0.8V*(1+1.24K/1K)=1.792V(VCC1V8_DAC)

Vout=0.8V*(1+R1/R2)=0.8V*(1+3.12K/1K)=3.296V(VCC3V3_DAC)

2片FPGA的DDR单元使用一片TPS51200。电路参考上节。

给FPGAREF电源的1.25V由固定输出LDO电源芯片REF3012提供,电路连接参考上节

给DAC芯片使用的VCP电源支持3.3V-5V输入,考虑到电压对性能的影响,采用可调LDOSGM2032-ADJ提供电源,初始电压为4.5V

计算公式如下:

VOUT=(R1+R2)/R2×0.8=(44.2K+1.91K+10K)/10K×0.8=4.488V

去耦电容XC7Z045-2FFG900I的去耦电容根据xilinx参考文档ug933-Zynq-7000-PCB如下:

XC7Z045-2FFG900IPL端去耦电容

XC7Z045-2FFG900IPS端的去耦电容

建议电容的封装如下:

XC7Z045-2FFG900I建议电容封装

其余芯片请参见各芯片Datasheet,无明确描述的,也请在电源入口处放置100nF电容滤波。

时钟单元时钟单元功能描述时钟单元提供单板正常工作需要的所有时钟,本板时钟的构成框图如下:

单板时钟组成框图

单板的时钟列表

芯片

数量

时钟属性

信号名

频率MHz

精度ppm

抖动ps

占空比%

上升/下降时间ps

电平/电压

88E1512

3

PS_PHY0_CLK_25M

PS_PHY1_CLK_25M

PL_PHY2_CLK_25M

25

50

200

32.5~67.5

3000

LVCMOS18

FPGA:XC7Z045-2FFG900I

1

FPGA_PS_33M333_CLK

FPGA_PL_33M333_CLK

33

50

NA

NA

NA

HCMOS3V3

FIBER_125M_CLK_P

FIBER_125M_CLK_N

125

50

NA

NA

NA

LVDS3V3

AD9518

1

ADC_REF_CLK_100M_P

ADC_REF_CLK_100M_N

100

25

NA

NA

NA

LVDS3V3

GD32F103CB

1

MCU_XTAL_8M_IN

MCU_XTAL_8M_OUT

8

50

NA

40~60

NA

NA

单板时钟方案设计板上时钟使用相应的Crystal或Oscillator。AD、DA部分的时钟在其相应章节进行描述。

复位方案设计单板复位框图

单板的复位框图如上所示。FPGA的上电复位可通过内部程序完成,也可通过外部按键SW3提供复位源,通过MAX811完成硬件复位。MSP430的复位可以通过内部的看门狗完成,也可以通过外部按键SW1完成。当FPGA与MSP430上电完成后,FPGA会通过IO口给MAX706喂狗,当FPGA程序跑飞,MAX706会传递给MSP430一个200ms的复位信号,MSP430收到信号后,判断当前情况,可复位FPGA程序。同时,这个复位也可由按键SW2完成。其余板上的3个PHY芯片、AD9518、AD9739以及板外的LCD都由FPGA控制复位。

硬件接口板上所有连接器详情如下表所示:

板卡端连接器选型表

Item

ManufacturePartNumber

Descriptoin

1

J-15022101

PCI连接器J1110PINTypeA5+1Rows,2mm*2mmSocket90°弯插

2

SSMA-KWHD

SSMA射频连接器90°弯插50Ω传输信号为1.6GHz

3

Ⅱ

Header1*32.54mm*2.54mm

4

Ⅱ

Header1*82.54mm*2.54mm

5

Ⅱ

Header2*72.54mm*2.54mm

6

J30J1-21ZKW-J

J30J1-21芯弯式焊板插座,印制板厚2mm,焊板针脚排列1.27mm×2.54mm,配P型锁紧附件。线缆须设计金属屏蔽丝网。

7

J30J1-21-TJ*-P-xxx

与上述J30J1-21ZKW-J插座配套使用的带线插头线缆,部分信号使用双绞线,信号定义如备注;线缆线长600mm,并配与插座的锁紧附件。线缆须设计金属屏蔽丝网。

8

J30J1-21-TJ*-P-xxx

与上述J30J1-21ZKW-J插座配套使用的带线插头线缆,线缆线长600mm,并配与插座的锁紧附件。线缆须设计金属屏蔽丝网。

9

J30J1-31ZKW-J

J30J1-31芯弯式焊板插座,印制板厚2mm,焊板针脚排列1.27mm×2.54mm,配P型锁紧附件。线缆须设计金属屏蔽丝网。

10

J30J1-31TJ*-P-xxx

与上述J30J1-31ZKW-J插座配套使用的带线插头线缆,线缆线长600mm,并配与插座的锁紧附件。线缆须设计金属屏蔽丝网。

11

J30J1-51ZKW

J30J-51芯的连接器,弯式焊板插座。

12

HJ30J-36ZKW

HJ30J-36芯的高速连接器,弯式焊板插座。

13

J30J1-9ZKW-J

J30J-9芯弯式焊板插座。

连接器信号分配表

序号

功能

连接器型号

是否保护

备注

1

千兆网络

3路

HJ30J-36ZKW

是

PS端两路,PL端一路,通过网络变压器后送出。

2

RS-422

4路

J30J1-51ZKW-J

是

PS端引出一路,PL端引出三路。转换芯片自带一定的保护功能

3

预留GPIO

24*GPIO

3

LCD

1路

J30J1-21ZKW-J

是

依据维信诺的LCD屏幕,将所有信号全部引出,使用TXS0108进行保护。

4

按钮信号

16*GPIO

J30J1-37ZKW-J

是

依据需求,预留16个GPIO信号,使用TXS0108进行保护。

5

LED

8*LED

是

依据需求,将PL端预留的6颗LED和MCU预留的2颗LED引出,使用TXS0108进行保护。

6

光纤接口

2路

HTS1302-LH

两路收发双向光纤。

7

模拟信号输入输出

5路

SSMA-KYWHD

模拟信号的输入输出,参考时钟的输入。

8

RS-232

1路

Ⅱ

排针,用于PL端的调试。

9

MCUJTAG

Ⅱ

排针,MCU的JTAG信号。

10

FPGAJTAG

Ⅱ

排针,FPGA的JTAG信号。

11

CPCIJ1

J-15022101

标准的CPCIJ1连接器。子卡端。

12

板端电源连接器

J30J1-9ZKW-J

DIP,用于单板的电源输入。

依据实际的功能需求,将各个功能接口的信号与连接器的脚位进行对应,其中插座为CPCI板端的连接器,插头A端与板端连接器连接,插头B端需要根据实际的使用和信号分配进行设计,在下面的各个表格中,B端均与A端相同。单板中千兆网络为标准的以太网信号;RS-422为标准信号;LED初始设计限流电阻为1K,电源为3.3V;LCD引出信号为LVTTL电平;GPIO信号在为特殊说明时,默认为LVTTL电平。

千兆网络信号分配表

RS-422与GPIO信号分配表

LCD信号分配表

按扭与LED信号分配表

电源输入连接器信号定义

软件接口PS侧、MCU接口指示灯形式向用户展示各个模块当前的工作状态

网络接口3个

RS422接口2个

RS232调试串口1个

提供PS端各个接口的驱动初始化接口,以及应用程序API接口,供二次开发使用。

FPGA接口I2C

GPIO

EMMC

DDR3

RGMII

FLASH

Layout指导分层结构PCB建议为12层板,板厚1.6mm。叠层请参考下图:

层叠建议参考

高速信号建议走TOP层和BOTTON层

整体布局布局请参考《CPCI_DXF_》。

走线规则请参考《CPCI_LAYOUTGUIDE_》

推荐阅读

-

万睿科技:革新贵阳智慧人居 小区里面的大智慧

随着新时代的智能科技发展,智能化正带来生产力提升。在5G时代浪潮的冲击下,要遵循人的生活需求、满足当代人对健康美好家的需求,应运而生的“智慧地产”的重要性不言而喻。科技加持,为人们打造出新一代全生命周期的生活能量场。智能化已经走进每一个贵阳人的生活中,生活中越来越多的智慧元素正扑面而来,为不断满足居...

-

“全面小康 追梦之路”调研行|科技之光点亮“现代桃花源”

交汇点讯9月24日,记者来到江苏省句容市天王镇戴庄村白沙自然村,村口南山脚下一片水稻田吸引了记者目光:和普通水稻相比,田里的稻杆矮、间隔大,稻穗还是青绿色。“这是著名农业专家赵亚夫新的研究成果——再生有机稻,8月中旬收完第一茬越光稻后留下30厘米稻梗,除灌水、除草外任其自然生长,11月下旬又能收一茬...

-

限幅器如何进行调整

限幅器是一种常见的音频设备,用于控制音频信号的幅度,以防止过载和失真。调整限幅器是确保音频信号在适当范围内的重要步骤。下面将介绍一些调整限幅器的基本步骤。首先,将限幅器连接到音频信号的路径上。这可以通过将音频信号源连接到限幅器的输入端口,然后将限幅器的输出端口连接到音频放大器或扬声器等设备来实现。确...

-

海南省发力冷链物流,宾通智能科技获投资,德国、埃及、东南亚均大笔投融资|物流投融资

7月5日-7月11日,据掌链不完全统计,国内外物流与供应链投融资市场发生8起相关品牌企业的投融资事件。国内物流与供应链1、近亿元!宾通智能科技完成A+轮融资7月8日,宾通智能科技有限公司获经纬创投(北京)投资管理顾问有限公司(领投)、苏州清流成长二期股权投资合伙企业(有限合伙)、杭州元璟投资管理有限...