PCB板有一种工艺,叫埋阻埋容,就是把贴片电阻,贴片电容放到PCB板里层去,这些贴片电阻电容一般都是很小的,比如0201,甚至更小的01005之类。这样做出来的PCB板跟正常的PCB板一样,但里面放了很多电阻电容,为了顶层,底层省出了不少元件摆放空间。

今天就给给大家讲讲这个埋阻埋容在CADENCEAllegro中如何设置。

1.PCB板外框设计。PCB外框需要画出物理外框、布线区域、器件放置区域,这几个是最重要的,有其他需要就添加其他的。

外框画好后就是开始画允许布线区域和允许期间放置区域

2.板层设置默认的时候只有顶层和底层,我们需要添加层,具体按自己的需求吧,我们这是6层。

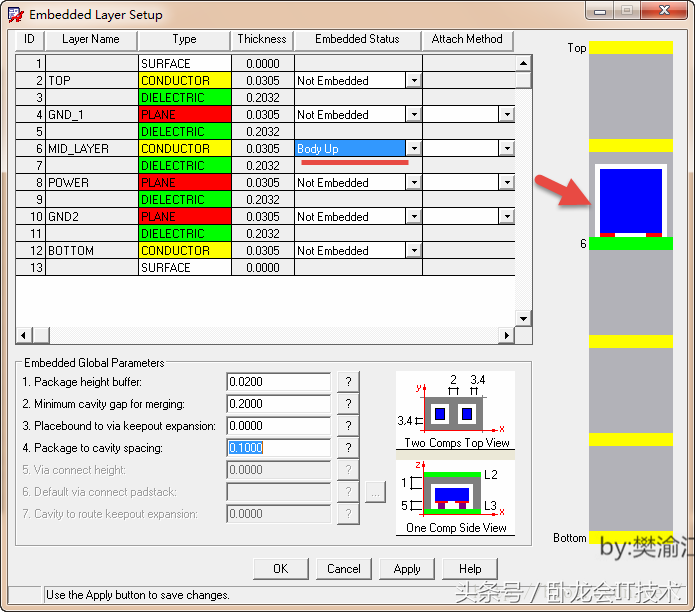

下图就是我针对我的PCB设置的板层结构。

层设置好了就需要对埋阻埋容进行设置

我们需要设置我们的第3层埋阻埋容,如下图

其中上半部分为叠层设置。

EmbeddedStatus设置埋入式器件状态,即设置内层器件方向;;

Bodyup表示器件在内导电层之上;

Bodydown表示器件在内导电层之下;

NotEmbedded表示该叠层不允许放置埋入器件;

ProtrudingAllowed表示允许器件凸起,即允许该内层下方或上方的导电层凸出本层,如下图所示。

AttachMethod用以设置埋入式器件的连接方式,包括:DirectAttach表示埋入式器件直接连接内电层;

IndirectlyAttach表示埋入式器件非直接连接上内电层,即以焊盘连接到内电层向外连接。

下半部分

EmbeddedGlobalParameters全局埋入式器件的叠层设置参数,其意义在右边的坐标中有对应显示,包括:Packageheightbuffer:定义埋入式器件腔体与相邻叠层的距离限制;

Minimumcavitygapformerging:定义腔体合成的最小距离,如25mil,即两个埋入式器件腔体间距接近至25mil以下时,两腔体即何为一个腔体;

Placeboundtoviakeepoutexpansion:定义器件的封装Placebound到器件外部禁止放置过孔区域的延伸距离;

Packagetocavityspacing:定义器件封装外部至埋入式腔体的间距;

Viaconnectheight:定义埋入式器件向外连接时,所用过孔的高度;

Defaultviaconnectpadstack:定义默认情况,允许和埋入式器件向外过孔相连接的焊盘类型;

Cavitytoroutekeepoutexpansion:定义埋入式器件腔体至该叠层禁止布线区域之间的间距。

3.器件设置左边是没有设置电阻电容可以埋入,右边是设置了电阻电容可以埋入。

具体设置如下:

在Embedded属性栏中,Placement列用以定义器件的埋入式属性,为某个器件定义Embedded/Placement属性,这些器件就可以在PCB中作为埋入式器件放入PCB内层,该属性包括:Option可选埋入式,则该器件可放在表面层,也可以作为埋入式器件放入内层;Required必要埋入式属性,则该器件必须作为埋入式器件放在内层,不可以置于表面层;ExternalOnly只外置属性,则该器件只能放在表面层,不可以作为埋入式器件置于内层。

4.放置器件如果放置器件的时候出现错误,没有器件跟着鼠标移动,那说明是你的库没有导进来。

以下是放置好后的器件

红色是顶层,蓝色是中间层了。

大功告成,顶层和中间层都放有器件。

如果两个期间像上图那样有重叠的时候,需要修改一下DRC,因为他默认二维空间里这两个器件重叠了,但是在三维空间里他们是没有重叠的。

把红线部分选成off就好了。

整个埋阻埋容的设计就OK了,剩下的就是布局布线了。这个我相信大家都能搞清楚的。